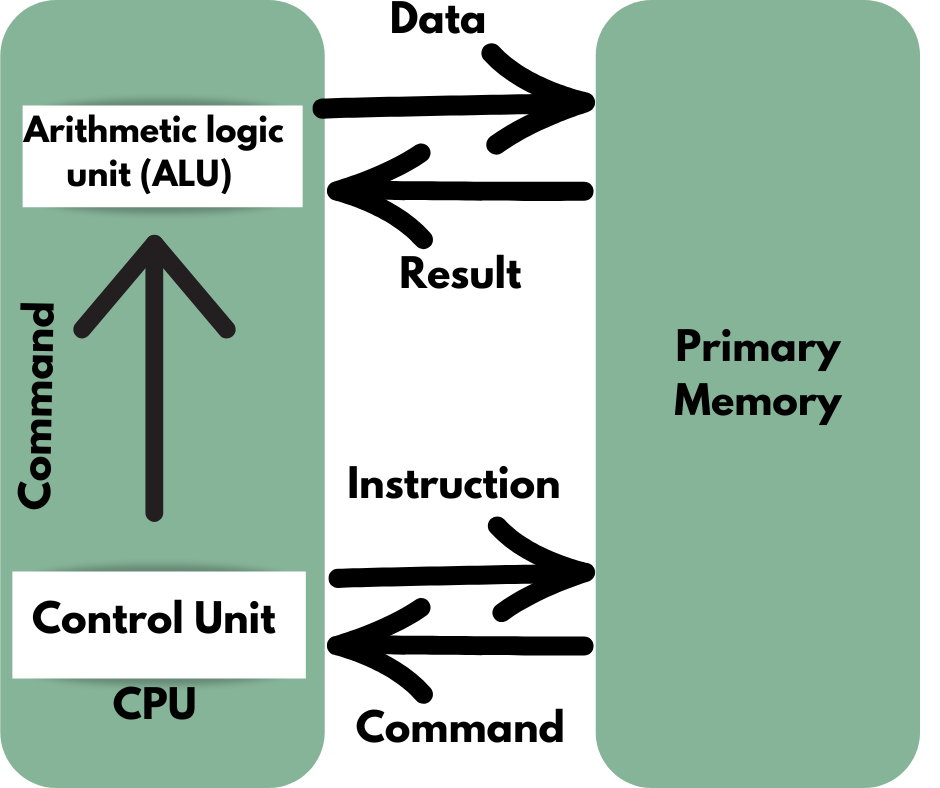

The control unit controls the traffic of the computer. It controls and coordinates the activities of the CPU. Just as the brain controls and coordinates the human body, the control unit controls and coordinates for the CPU.

The job of the control unit is to manage all the computers. The control unit itself operates according to the stored instructions in ROM and RAM. That is, it commands all other parts of the computer to operate according to the instructions stored in RAM. But the control unit cannot do anything without main memory instructions. Again, according to the instructions in the control unit, the ALU completes the mathematical processes such as addition, subtraction, etc. That is, the ALU turns the instructions of the control unit into action. On the other hand, the rider functions more like the primary memory of the pilot control unit (PCU) and the plane functions more like the ALU when the pilot navigates the rider to the destination in accordance with the instructions.

Activities of CPU’s Control Unit:

- In the IF stage, the PC fetches the next instruction from memory and is then incremented to the next instruction.

- Data and instruction flow within the CPU are managed by Execution Control (EC).

- Fetching instructions one by one from main memory.

- Manage instruction flow in pipelined architectures, handle hazards such as data dependencies, and control hazards.

- Predict the outcome of branch instructions to reduce the performance impact of conditional branches. Subsequently, fetch and execute instructions based on branch predictions.

- Manage power consumption based on workload requirements. Implement dynamic voltage and frequency scaling (DVFS) techniques to adjust the CPU’s operating voltage and frequency dynamically.

- The arithmetic logic unit (ALU) commands to perform any operations such as addition, subtraction, etc. according to this calculation instruction.

- The calculation result of the ALU is sent to the main memory.

- Bringing programs from input and auxiliary memory to main memory.

- To handle exceptional conditions during program execution, transfer control to an appropriate exception handler after suspending the normal execution flow and saving the current CPU context.

All of these responsibilities work together to give the control unit the ability to efficiently manage CPU resources and coordinate program execution, ensuring timely and accurate execution of instructions while optimizing CPU power.

Structure of CPU’s Control Unit:

One of the most important parts of a CPU is the control unit (CU), which is in charge of controlling how instructions are carried out and directing the actions of other CPU components. The architecture and design of the CPU can affect the control unit’s structure, but the following general structure includes many common components:

- Instruction Fetch (IF) Unit:

A key part of the CPU that is in charge of obtaining instructions from memory is the Instruction Fetch (IF) Unit. It retrieves the instruction from memory after determining the address of the subsequent instruction to be performed, frequently by using the Program Counter (PC). The following step of the pipeline receives this fetched instruction for decoding and execution. To maximize CPU performance and maintain a constant flow of instructions, the IF unit must operate efficiently.

- Instruction Decode (ID) Unit:

During the Instruction Decode (ID) Unit stage, the fetched instructions are decoded to determine the operation to be performed and the operands involved. The opcode and operand fields are extracted from the instruction word. This may involve decoding complex instruction formats and translating them into micro-operations.

- Control Logic Unit:

The Control Logic Unit is responsible for generating control signals by decoding instructions and assessing the current state of the CPU. It coordinates the activation of specific functional units within the CPU, including the arithmetic logic unit (ALU), memory unit, and input/output (I/O) interfaces. Additionally, it manages the flow of data and control signals throughout the CPU.

- Execution Unit:

The Execution Unit performs specified operations on data operands, using the ALU for arithmetic and logical operations, the FPU for floating-point operations, and SIMD units for vectored operations. It interfaces with the register file and other data paths to access operands and store results.

- Branch Prediction Unit:

The Branch Prediction Unit predicts branch instructions to improve performance and maintain pipeline throughput. It may include BTBs and branch history tables to store prediction information.

- Exception Handling Unit:

The Exception Handling Unit manages exceptional conditions during instruction execution, such as interrupts, traps, and faults. It suspends normal execution, saves the CPU state, and transfers control to an appropriate handler. It also manages communication with peripheral devices and external interrupts.

- Timing and Clock Circuitry:

Clock and Timing Circuitry generates and distributes clock signals to synchronize the operation of various components within the CPU. It includes phase-locked loops (PLLs) and clock distribution networks to ensure precise timing and control.

- Circuitry for power management:

Power management circuitry manages power consumption based on workload requirements and implements dynamic voltage and frequency scaling (DVFS) techniques to adjust the CPU’s operating voltage and frequency dynamically for power savings.

The control unit’s architecture is based on the CPU’s architectural objectives and the intended applications. Its functions include handling exceptions, managing resources, executing instructions, and optimizing power and performance.